STM32单片机:深入剖析STM32的时钟系统

- STM32单片机开发

- 2024-11-14

- 636热度

- 0评论

时钟系统在单片机中的作用,就如同心脏脉搏对人体至关重要一样,其重要性不言而喻。STM32的时钟系统相较于简单的51单片机而言,显得异常复杂,无法仅凭一个时钟系统就解决所有问题。这对STM32初学者来说无疑是一个挑战。本文旨在深入剖析STM32的时钟系统,帮助读者透彻理解其背后的运行原理。

时钟的概念

单片机时钟是由晶振产生的,晶振在通电后会产生一个固定频率的振荡信号,这个信号就是单片机时钟的源头。单片机通过这个时钟信号来控制内部的各个部件,确保它们能够协同工作,完成各种复杂的任务。

时钟信号对单片机来说非常重要,没有时钟信号,单片机就无法正常工作。因为单片机需要按照一定的时序来执行指令、传输数据等操作,而这些操作都需要时钟信号来同步和协调。

时钟信号在单片机中就像人的心跳一样,推动着单片机内的各个部分按照既定的节奏执行相应的指令。无论是处理器内核的指令执行,还是外设部件的数据传输与转换,都离不开时钟信号的驱动。一旦时钟信号出现问题,单片机将无法正常执行指令,整个系统将陷入混乱状态。

时钟树与时钟源

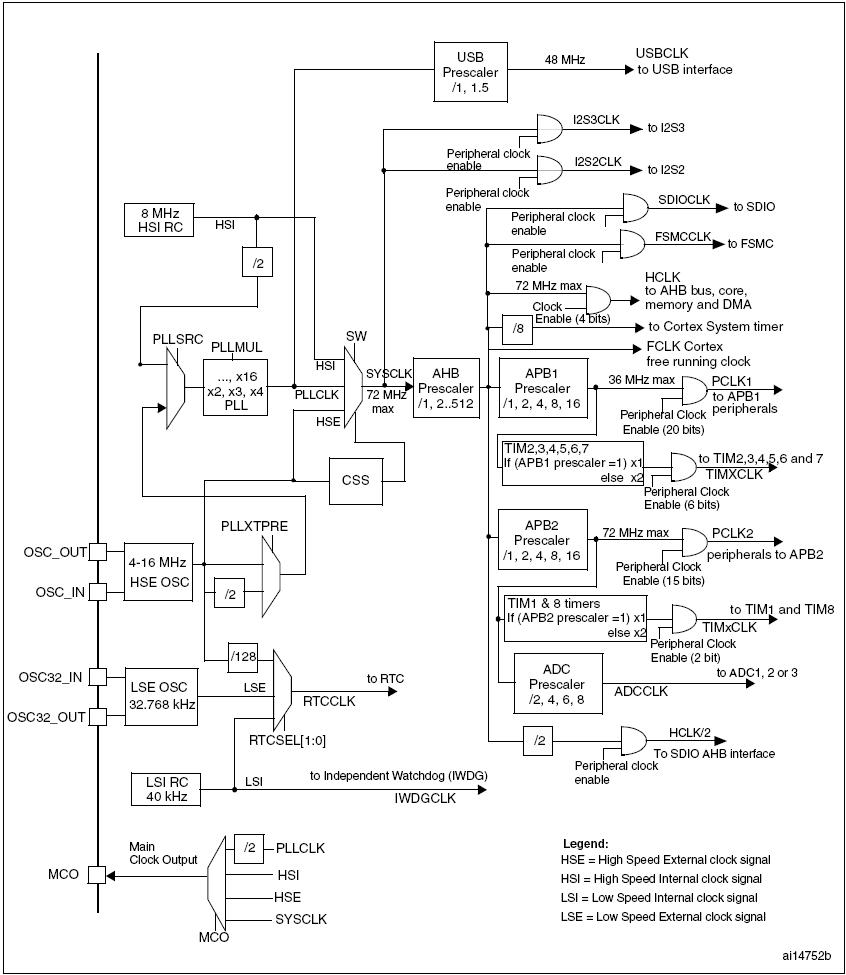

上图是STM32F1xx系列时钟树。时钟树决定了单片机各个部分的工作频率和时序。简单来说,时钟树就像是一个大树,树干是系统时钟,树枝是各个外设的时钟,而树叶则是具体的工作频率。时钟树说明了STM32的时钟走向,从时钟源一步步分配到外设时钟。

从时钟频率来说,又分为高速时钟和低速时钟,高速时钟是提供给芯片主体的主时钟,低速时钟只提供给芯片的RTC(实时时钟)及独立看门狗使用。

从时钟源头来说,又分为内部时钟源和外部时钟源,内部时钟源是由芯片内部RC振荡器产生的,外部时钟信号是由外部的晶振输入的。单片机启动后,默认使用内部时钟源。

STM32F1xx系列单片机的时钟源有多个,主要包括:

HSI(高速内部时钟):这是由单片机内部产生的时钟,频率固定,但精度相对较低。

HSE(高速外部时钟):这是通过外部晶振产生的时钟,频率和精度都可以根据需要进行调整。

LSI(低速内部时钟):这是由单片机内部产生的低速时钟,主要用于驱动一些低速外设或作为看门狗的时钟源。

LSE(低速外部时钟):这是通过外部晶振产生的低速时钟,主要用于为RTC(实时时钟)提供时钟源。

高速外部时钟

我们以最常用的高速外部时钟(HSE)为例分析,假定外部晶振提供的频率为8MHZ。

(1)高速外部时钟外接两个引脚OSC_IN和OSC_OUT,这两个引脚接外部晶振电路,引入8MHZ的固定时钟信号;

(2)8MHZ的时钟进入PLLXTPRE分频器(对高速外部时钟(HSE)进行预分频的电路,主要功能是降低HSE的频率,以满足后续电路(如锁相环PLL)的输入要求),在这个分频器中,可以通过寄存器配置来选择输出时钟信号的频率。它的输出频率可以是对输入时钟的二分频或不分频,若配置为不分频,PLLXTPRE分频器输出的时钟还是8MHZ;

(3)8MHZ的时钟进入PLLSRC(用于选择PLL的输入时钟源),同时HSI(高速内部时钟)也进入PLLSRC,可以通过寄存器来配置来选择输出高速外部时钟还是高速内部时钟。若选择高速外部时钟,PLLSRC将输出高速外部时钟;

(4)8MHZ的时钟进入PLLMUL(通过配置PLLMUL的值,可以改变PLL的输出时钟频率),在这里可以配置PLLMUL的倍频因子,输出不同的时钟频率,经过PLL倍频的时钟称为PLLCLK。若倍频因子设置为9倍频,时钟将从8MHZ的频率倍频为72MHZ;

(5)PLLCLK时钟进入SW开关,同时HSI和HSE也进入SW开关,通过这个开关可以切换输出的时钟,可以选择输出PLLCLK时钟,也可以选择输出HSI或HSE时钟,经过SW开关之后的时钟就是STM32的系统时钟SYSCLK,若选择输出PLLCLK时钟,SYSCLK的时钟频率就是72MHZ;

(6)SYSCLK经过AHB预分频器,分频后再输入到其它外设;

(7)GPIO外设是挂载在APB2总线上,APB2的时钟是APB2预分频器的输出,APB2预分频器的输入来自AHB预分频器,若AHB预分频器设置为不分频,则GPIO的时钟为72MHZ。

一些与开发相关的时钟

在对高速外部时钟分析的过程中,我们得到了几个相关的时钟,下面对这些时钟做一个简单介绍。

SYSCLK:系统时钟,是STM32大部分部件的时钟来源,主要由AHB预分频器分配到各个部件。

HCLK:为连接在AHB总线上的外设提供时钟信号。AHB总线通常连接高速外设,如内存、NAND、LCD控制器等。

FCLK: 由AHB预分频器输出得到,为CPU内核提供时钟信号,FCLK的频率直接决定了CPU的主频,即CPU时钟周期是1/FCLK。

PCLK1:由AHB1预分频器输出得到,在STM32F103等型号中,PCLK1的最大频率为36MHz,因此常通过设置分频使PCLK1等于HCLK的一半,以满足这一要求。PCLK1主要用于为APB1总线上的外设提供时钟信号,如UART、SPI等低速外设,以支持它们的正常工作。

PCLK2:由AHB2预分频器输出得到,最高频率可达72MHz,主要用于为APB2总线上的高速外设提供时钟信号。

STM32为什么需要对输入的时钟信号进行倍频和分频?

STM32微控制器拥有众多外设,其中部分高速外设(如高级定时器、SDIO等)需要更高的时钟频率以支持其高速运行,倍频技术能够提供这些高速外设所需的时钟频率。部分低速外设(如UART、SPI等)仅需较低的时钟频率即可满足其运行需求。通过分频技术,可以降低时钟频率以适应这些低速外设。

持续为STM32提供高频时钟会增加其功耗。在不需要使用高速外设时,通过分频技术降低时钟频率,有助于减少功耗,延长设备的使用寿命。

直接提供高频时钟信号(如72MHz)给电路板,可能会增加制作难度。通过倍频技术,可以从较低的外部时钟频率(如8MHz)开始,逐步提升至所需的高频时钟,从而降低电路板设计难度。