了解STM32单片机的系统架构

- STM32单片机开发

- 16天前

- 93热度

- 0评论

了解STM32单片机的系统架构,就是明确这颗芯片在硬件上由哪几部分构成?各部分的功能以及各部分之间的数据交换,对STM32单片机系统架构的把握,有助于我们进行单片机的开发。

系统架构

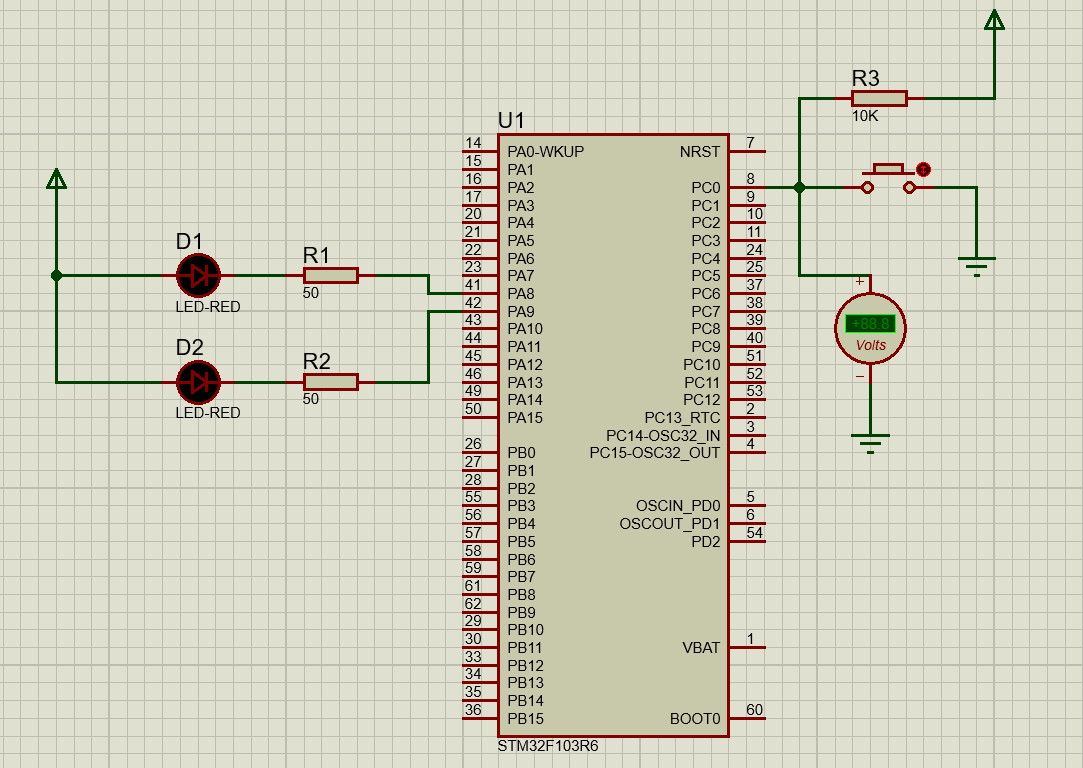

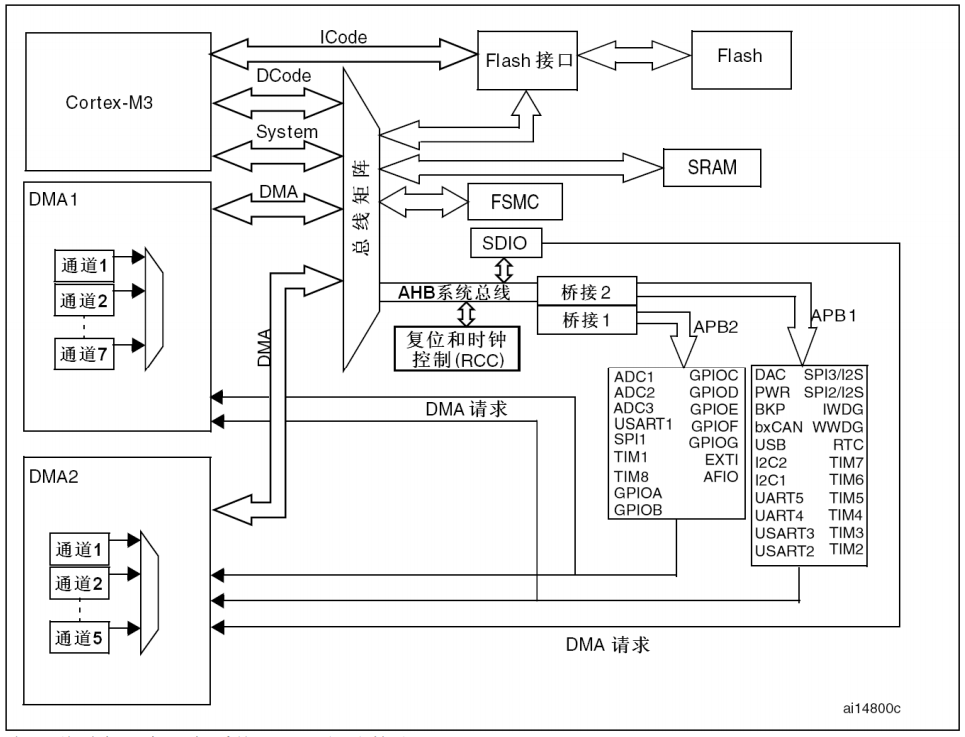

STM32单片机系统(互联型除外)由四个驱动单元和四个被动单元构成,互联型STM32单片机有五个驱动单元,多一个以太网驱动单元。下图是STM32单片机(非互联型)的系统架构图:

Cortex-M3内核是单片机的核心结构,内核由ARM公司设计研发,芯片厂商要生成基于ARM架构的Cortex-M3内核的单片机,需要得到ARM公司的授权。M3内核、DCode总线、System总线和DMA构成了四个驱动单元。

M3内核是基于ARMv7架构的ARM嵌入式内核,内核设计没有采用冯诺依曼结构,而是采用了哈佛结构。学过计算机的都知道冯诺依曼结构,现在大多数计算机都采用了冯诺依曼结构,该结构将程序指令和数据存储到一个存储器,内部没有总线。哈佛结构使用两个独立的存储器模块,分别存储指令和数据,并使用指令总线和数据总线分别与指令存储器和数据存储器通信。因为指令和数据分别使用独立的总线,因此M3内核的执行效率非常高效。另外,M3内核通过数据总线和系统总线挂载存储器、外设、DMA控制器等设备,从而构成了高效能的STM32单片机。

总线是M3内核与存储器、外设、DMA控制器等设备传输信息的公共数据通道。例如:内核的指令总线(ICode),将内核、Flash接口(闪存存储器读写接口)、Flash(闪存存储器)连接在一起,建立数据通路,内核应用指令总线通过Flash接口读取Flash存储器内的程序指令。与总线相关的主要参数有总线宽度、总线频率和总线带宽。总线宽度是指总线能同时传输的数据位数, 如8位、32位、64位;总线频率是指总线的工作速度,频率越高,速度越快;总线带宽用来描述总线传输数据的快慢,总线带宽=总线宽度x总线频率/8,单位为MB/s。

DCode总线是数据总线,用于内核、存储器、外设之间的数据通信。System总线是内核系统总线,用于内核、存储器、外设之间的信息传输。

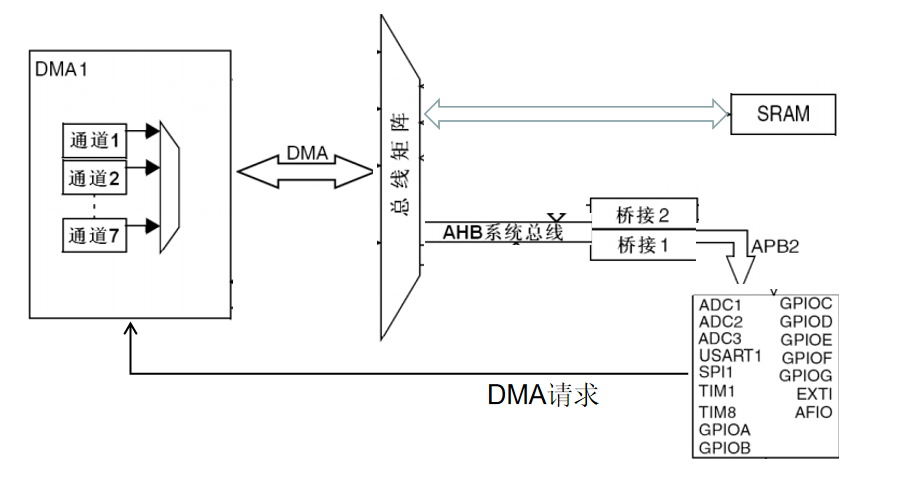

STM32单片机提供了两个DMA控制器,分别是DMA1和DMA2。DMA为STM32单片机提供了与外部设备进行高速数据传输的通道,DMA可以绕过M3内核与外部设备、内存之间直接进行数据传输,无需M3内核的控制。当外部设备需要通过DMA传输数据到内存时,外设先给DMA控制器发送DMA请求,DMA收到请求信号之后,控制器会给外设一个应答信号,当外设应答后且DMA控制器接收到应答信号之后,就会启动DMA传输,直到传输完毕。DMA传输过程如下图所示:

上图的总线矩阵负责阵协调内核系统总线和DMA主控总线之间的访问仲裁,仲裁利用轮换算法,即协调内核系统总线和DMA总线对存储器、外部设备的访问权,访问权每隔一段时间就更换。AHB系统总线是高性能总线,它可以将M3内核、高速外部设备(如SRAM存储器)、DMA控制器等连接在一起,构建高性能的数据传输通道。AHB总线不能直接连接低速外部设备(如USART、ADC等外设),因此需要通过AHB/APB桥将AHB总线结构转换为APB总线结构,低速外部设备通过APB总线接入到单片机,APB总线主要用于和低速以及低功耗的外设通信,APB1操作速度限于36MHz,APB2操作于全速(最高72MHz),单片机的GPIO端口都挂载到APB2总线。

单片机的四个被动单元依次是Flash、SRAM、FSMC、AHB/APB桥,它连接所有的APB设备。Flash存储器断电后不会丢失存储的内容,因此它主要用于存储在单片机运行的程序指令,当然也可以存储一些单片机的关键数据。SRAM是静态随机存储器,断电后会丢失存储的内容,一般用于存储程序运行期间的数据信息。FSMC是静态存储控制器,它可以让STM32单片机接入不同类型的外部静态存储器,轻松实现单片机内存的扩展。

被动单元为单片机的片上资源,片上资源又分为系统资源和外设资源。系统资源指维持单片机正常工作或保证单片机正常工作的一些资源,如系统运行所必须的时钟、防止系统死机的看门狗。外设资源往往用于满足单片机系统的业务需要,通过硬件实现与外部设备高效的通信或操作,如模数转换器、串行通信等外部设备等。

要使用单片机的一个外设设备,需要先配置外设的相关寄存器,再通过GPIO端口与外设设备连接,当外设存在大量数据传输的需求时,使用M3内核会增加内核的负担,这时DMA可以提供数据传输的通道,在不需要内核干预的情况下完成数据的传输。

存储器组织

STM32单片机的存储器包括程序存储器、数据存储器、寄存器和输入输出端口,它们被组织在同一个4GB的线性地址空间内。为什么是4GB的线性地址空间呢?因为STM32的总线宽度是32位,可寻址空间为4GB。

数据以小端模式存放在存储器中,小端模式就是把数据的低位保存在内存的低地址中,而数据的高位保存在内存的高地址中。与小端模式对应的是大端模式,大端模式把数据的低位保存在内存的高地址中,数据的高位保存在内存的低地址中。为什么会有大小端模式之分呢?这是因为在计算机系统中每个存储单元对应一个字节,但是编程语言的数据类型一般对应着多个字节(如C语言的整型、浮点类型等),当存储器存储多个字节时,就需要解决字节的顺序问题,大端模式和小端模式就时解决字节存储顺序问题的。例如:一个C语言无符号短整型变量的值为0x1122(0x11为高字节,0x22为低字节),存储在内存地址为0x0010的存储单元内,0x0010存储0x22,0x0011存储0x11。

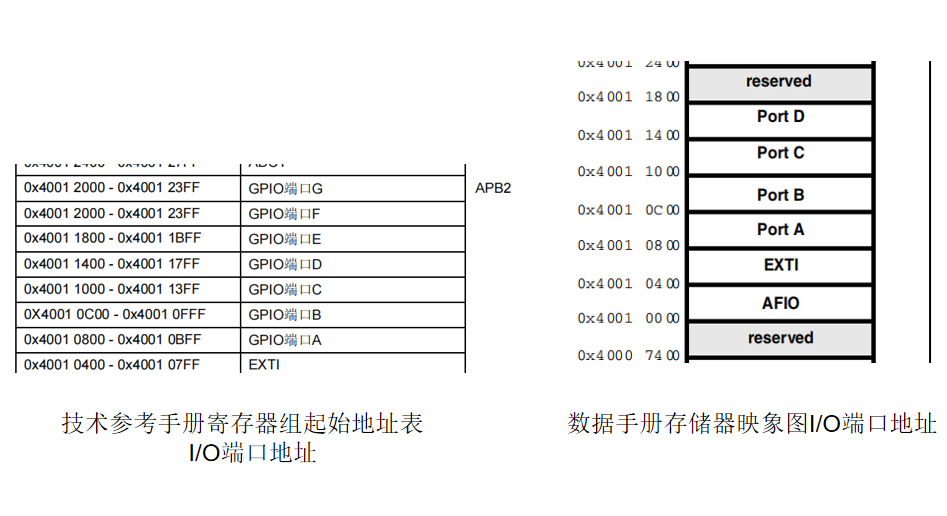

本课教学使用的是STM32F103R6型单片机,与之配套的数据手册给出了存储器映像图,若同学们使用的其它型号,请参考与之配套的数据手册。存储器映像就是告诉我们STM32是如何分配4GB存储空间给Flash、SRAM、M3内核寄存器、外设(寄存器、内存等存储器)等设备。对于STM32F103R6型单片机,观察存储器影像图,外设存储地址范围:

0x4002 3400~0x4000 0000

上图是《STM32技术参考手册》寄存器组起始地址表,与《TM32F103R6数据手册》存储器映象图,关于I/O端口存储空间的对比图。《TM32F103R6数据手册》的PortA对应《STM32技术参考手册》GPIO端口A,PortB对应GPIO端口B,……,它们的起始地址都是相同的。

在《stm32f10x.h》文件中,跟踪GPIOA的宏定义,可以找到外围设备基地址的宏定义PERIPH_BASE,基地址为0x40000000。Flash、SRAM、外围设备基地址的宏定义如下图所示:

GPIO端口挂载在APB2总线上,APB2总线基地址的宏定义为:

![]()

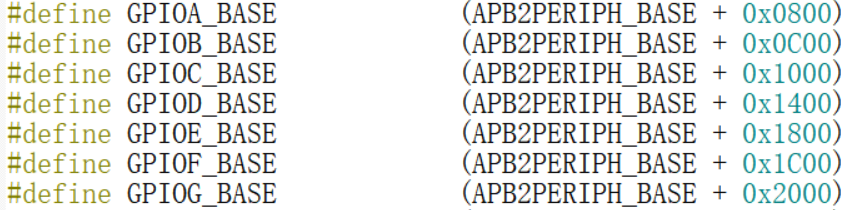

最后可以找到GPIOxBASE的宏定义:

STM32开发者可以通过GPIO端口的宏定义,找到GPIO组寄存器的基地址,并对GPIO寄存器进行读写操作。通过类似的方式,我们就可以给具体的寄存器写上适当的参数来控制STM32了。